-

業種・地域から探す

続きの記事

半導体産業

半導体最新パッケージングを支える日本メーカー

【執筆】 いちよし経済研究所 企業調査部 シニアアナリスト 大澤 充周

AI(人工知能)の本格普及に伴うデータ流通量の爆発的な拡大を受け、半導体業界に対し、より大量かつ高速なデータ処理が可能な技術進化が求められている。これまでの微細化に加え、近年急速にニーズが高まりつつあるパッケージング(特に3次元実装のチップレット)の動向と、それを支える日本メーカーの取り組みについて紹介していく。

「チップレット」インターポーザーに実装

米オープンAIの「ChatGPT」に象徴される生成AIが急速に普及しつつある。生成AIの核となるのが米エヌビディアの画像処理半導体(GPU)だが、生成AIはGPUだけでなく、広帯域メモリー(HBM)などが混載されて作動する。

この混載工程がパッケージングであり、半導体の高性能化のカギとなっている。これまで半導体は回路線幅の微細化ロードマップに沿って進化してきたが、パッケージング、特に先端3次元実装であるチップレットが脚光を浴びている。

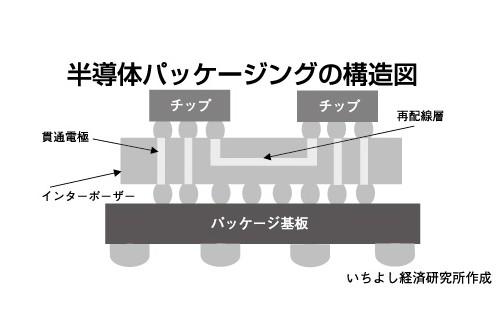

チップレットとは1チップ内にさまざまな半導体を混載するSoC(System on a chip)に対し、インターポーザーと呼ばれる基板にチップを実装する方法を指す。チップレットのメリットは先端ラインで製造すべき半導体と非先端ラインでも製造可能な半導体を別々に製造できることによるコストメリットがある。また、1チップ上に半導体を収める必要がないため、個々の半導体の製造を専門ノウハウを持つ別々のメーカーで行うことによる開発期間の削減と開発コストの低減などが期待できる。

TSMC・ラピダス/チップレット競演

TSMCが手がける2・5D(2・5次元)パッケージと呼ばれるCoWoSもチップレットの一形態と言える。また2025年に試作ラインを立ち上げる日本のラピダスも、新エネルギー・産業技術総合開発機構(NEDO)の旗振りの下で米IBMと組み、2ナノメートルノードの半導体用チップレット技術の確立を目指す取り組みをスタートさせている。

チップレットの特徴は各チップを一つの半導体として接合するインターポーザーと呼ばれる基板が使用されることである。インターポーザーを介して各チップが接合され、それがパッケージ基板に実装される。

インターポーザーはチップレットの要とも言えるパーツであり、配線密度の向上や多層化、大型化や低コスト化など、さまざまな要求を満たす必要がある。これらはチップレットの成否を決定する技術面でのカギと言うことができよう。

ここでカギとなるインターポーザーでは、半導体前工程の技術が応用されつつある。回路形成にはリソグラフィー技術が用いられ、露光の感光材として用いられるフォトレジストでは東京応化工業が戦略的な展開を行っている。

後工程、高まる重要度

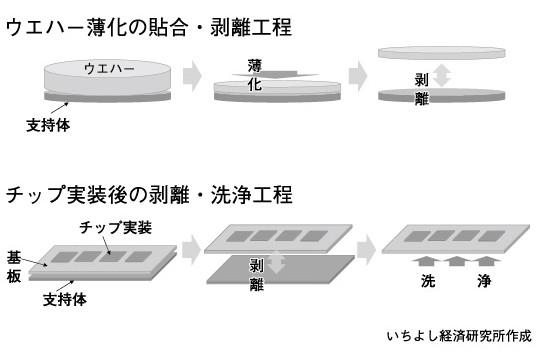

インターポーザーに半導体チップを実装する工程では、製造装置メーカーの活躍が期待されている。ウエハーハンドリングシステムと呼ばれるインターポーザー部材のシリコンウエハー研磨・薄板化工程において、ガラスキャリアをシリコンウエハーに貼付・剥離するための装置を手がけるのがAIメカテックである。同社の顧客は台湾や中国の半導体メーカーや半導体後工程請負業(OSAT)であり、インターポーザーを使用する生成AI用半導体の需要が大きく伸びている。AIメカテックと同様の製品ながら2・5Dパッケージにおいて実装時に使用される支持体とウエハーの剥離・洗浄を行う装置を製造しているのがタツモである。

そして生産効率向上に不可欠なのが、樹脂封止装置世界トップのTOWAである。同社は樹脂コントロール(レジンフローコントロール)ノウハウを蓄積していることから、保護過程で行われるキャピラリー・アンダーフィルと呼ばれる工程を省くことにより生産効率と放熱性を向上させることができ、28年3月期以降に受注が本格化する可能性が高いと当経済研究所では想定している。

チップレットの普及により、半導体後工程メーカーの重要度が高まることに加え、前工程関連メーカーにもビジネス機会が生じる。今後、同分野が半導体業界の主戦場の一つとして存在感が高まってくるだろう。